Back POWER4 Esperanto POWER4 French POWER4 Hungarian POWER4 Italian POWER4 Japanese POWER4 NB POWER4 Portuguese POWER4 Romanian POWER4 Russian POWER4 Ukrainian

POWER4 SCM | |

| General information | |

|---|---|

| Launched | 2001 |

| Designed by | IBM |

| Performance | |

| Max. CPU clock rate | 1.1 GHz to 1.9 GHz |

| Cache | |

| L1 cache | 64+32 kB/core |

| L2 cache | 1.41 MB/chip |

| L3 cache | 32 MB off chip |

| Architecture and classification | |

| Technology node | 180 nm to 130 nm |

| Instruction set | PowerPC (PowerPC v.2.00/01) |

| Physical specifications | |

| Cores |

|

| History | |

| Predecessors | POWER3, RS64 |

| Successor | POWER5 |

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

| Cancelled in gray, historic in italic |

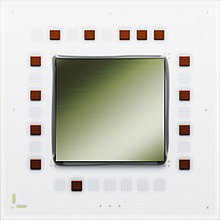

The POWER4 is a microprocessor developed by International Business Machines (IBM) that implemented the 64-bit PowerPC and PowerPC AS instruction set architectures. Released in 2001, the POWER4 succeeded the POWER3 and RS64 microprocessors, enabling RS/6000 and eServer iSeries models of AS/400 computer servers to run on the same processor, as a step toward converging the two lines. The POWER4 was a multicore microprocessor, with two cores on a single die, the first non-embedded microprocessor to do so.[1] POWER4 Chip was first commercially available multiprocessor chip.[2] The original POWER4 had a clock speed of 1.1 and 1.3 GHz, while an enhanced version, the POWER4+, reached a clock speed of 1.9 GHz. The PowerPC 970 is a derivative of the POWER4.

- ^ "IBM's Server Processors: The RS64 and the POWER". The CPU Shack Museum. 2011-01-24. Retrieved 2015-04-17.

- ^ William Stallings, Computer Organization and Architecture, Seventh Edition, -pp 44

© MMXXIII Rich X Search. We shall prevail. All rights reserved. Rich X Search